### CryptAttackTester: formalizing attack analyses

Daniel J. Bernstein\* University of Illinois at Chicago USA Ruhr University Bochum Germany Tung Chou\* Academia Sinica Taiwan

### **Abstract**

Quantitative analyses of the costs of cryptographic attack algorithms play a central role in comparing cryptosystems, guiding the search for improved attacks, and deciding which cryptosystems to standardize. Unfortunately, these analyses often turn out to be wrong.

Formally verifying complete proofs of attack performance is a natural response but crashes into an insurmountable structural problem: there are large gaps between the best proven cost among known attack algorithms and the best conjectured cost among known attack algorithms. Ignoring conjectured speedups would be a security disaster.

This paper presents a case study demonstrating the feasibility and value of successfully formalizing what state-of-the-art attack analyses actually do. The input to this formalization is not a proof, and the output is not a formally verified proof; the formalization process nevertheless enforces clear definitions, systematically accounts for all algorithm steps, simplifies review, improves reproducibility, and reduces the risk of error.

Concretely, this paper's CryptAttackTester (CAT) software includes formal specifications of (1) a general-purpose model of computation and cost metric, (2) various attack algorithms, and (3) formulas predicting the cost and success probability of each algorithm. The software includes general-purpose simulators that systematically compare the predictions to the observed attack behavior in the same model. The paper gives various examples of errors in the literature that survived typical informal testing practices and that would have been immediately caught if CAT-enforced links had been in place.

The case study in CAT is information-set decoding (ISD), the top attack strategy against the McEliece cryptosystem. CAT formalizes analyses of many ISD algorithms, covering interactions between (1) high-level search strategies from Prange, Lee–Brickell, Leon, Stern, Dumer, May–Meurer–Thomae, and Becker–Joux–May–Meurer; (2) random walks from Omura, Canteaut–Chabaud, Canteaut–Sendrier, and Bernstein–Lange–Peters; and (3) speedups in core subroutines such as linear algebra and sorting.

#### 1 Introduction

There is a long history of critical flaws in analyses of the performance of algorithms to attack cryptosystems. For example:

• The 1984 Schnorr–Lenstra factorization algorithm [109] was, in the words of 1992 Lenstra–Pomerance [79, page 484], "the first factoring algorithm of which the expected running time was conjectured to be  $L_n[\frac{1}{2}, 1 + o(1)]$ , and it is now also the first algorithm for which that conjecture must be withdrawn".

- 2010 Howgrave-Graham–Joux [67] claimed "we can solve 1/2-unbalanced knapsacks in time  $\tilde{O}(2^{0.3113n})$ ", and backed this up with a detailed algorithm analysis [67, Section 4]. However, in 2011, Becker–Coron–Joux [15, Section 2] reported that May and Meurer had found a mistake in [67], and that correcting this mistake changed 0.3113 to 0.337.

- 2017 Chailloux–Naya-Plasencia–Schrottenloher [44] stated that a generic quantum algorithm to find n-bit collisions had "a time-space product of  $\tilde{O}(2^{12n/25})$ ", outperforming the well-known n/2 exponent for non-quantum parallel algorithms. However, Bernstein [21] pointed out that this 12n/25 was a calculation error: the time-space product for the algorithm actually has exponent 13n/25, above n/2.

- 2019 Esser-May [56] claimed subset-sum exponent 0.255, improving upon the best previous exponent (namely 0.291 from [15], improving upon the aforementioned 0.337). Three months later, a comment "Issue with counting duplicate representations" was added and the paper was withdrawn.

- 2019 Ducas–Plançon–Wesolowski [53, Figure 5] graphed performance of an asymptotically useful quantum algorithm to attack Ideal-SVP, and drew the "reassuring" conclusion that "the cross-over point with BKZ-300 should not happen before ring rank  $n \approx 6000$ ". In 2021, an online update of [53] radically revised the graph and changed "6000" to "2000", crediting a six-person team for discovering a critical sign error inside the underlying attack analysis.

For [56], the error was caught at the preprint stage. For each of the other examples, the error was in a peer-reviewed paper in a high-profile publication venue. Many more examples are known.

The positive view is that each of these examples shows the scientific community successfully identifying and correcting an error. It is nevertheless concerning to see one example after another of an error playing a critical role in an announced attack analysis and not being caught until later, sometimes years later. Even more concerning is that today's processes for catching these errors are informal and haphazard; presumably the *known* error rate is an underestimate of the *actual* error rate. This procedural deficiency leaves real-world cryptography vulnerable to an important class of attacks; see Appendix A.

<sup>&</sup>lt;sup>1</sup>Both authors contributed equally to this research. Author list in alphabetical order; see https://www.ams.org/profession/leaders/culture/CultureStatement04.pdf. This work was funded by the Intel Crypto Frontiers Research Center; by the Deutsche Forschungsgemeinschaft (DFG, German Research Foundation) as part of the Excellence Strategreemeinschaft (DFG derman Federal and State Governments—EXC 2092 CASA—390781972 "Cyber Security in the Age of Large-Scale Adversaries"; by the U.S. National Science Foundation under grant 1913167; by the Taiwan's Executive Yuan Data Safety and Talent Cultivation Project (AS-KPQ-109-DSTCP); and by the Taiwan's National Science and Technology Council (NSTC) grant 109-2222-E-001-001-MY3. Date of this document: 2023.06.14.

1.1. The obvious path to high assurance, and why the path fails for cryptanalysis. See [14] for a survey of exciting progress in formalization and automated verification of proofs, including security proofs for cryptographic protocols and correctness proofs for cryptographic software. It is natural to ask whether formally verified proofs can also address the deluge of errors in security analysis of the underlying mathematical primitives.

The obvious strategy to formally verify a proof of the effectiveness of any particular attack, where effectiveness is defined as the pair (success probability, cost), is as follows:

- Fully specify the model of computation and a cost metric.

- Fully specify the problem under attack.

- Fully specify the attack algorithm in the model of computation.

- Fully specify the formula for the predicted cost of the algorithm.

- Fully specify the formula for the predicted success probability of the algorithm.

- Fully specify the proof that the algorithm matches these predictions.

- Have a computer verify each step in the proof.

The first five steps are formally *stating* the claim of attack effectiveness. The sixth step takes the existing informal proof of the claim and turns it into a formal proof. The last step eliminates errors more reliably than humans do; this step requires all of the specifications to be in languages whose semantics are understood by the computer.

But what happens if the existing attack analysis isn't an informal proof, but merely a conjecture? The analyses mentioned above from [109], [67], [15], [56], and [53], for factorization and subset sum and Ideal-SVP, never claimed to be theorems: they are a different kind of science, relying on estimates and heuristics and experiments. Some *fragments* of the analyses had proofs (see, e.g., [67, Corollary 5]), but the errors were outside these fragments.

Similar comments apply to state-of-the-art attacks against many other cryptographic problems. The best proven effectiveness among known attacks is usually far worse than the best conjectured effectiveness among known attacks: see, e.g., [67] saying that 0.385 is the best exponent "for which we can prove the algorithm" but conjecturing that the algorithm reaches 0.3113. Focusing on proven effectiveness would, conjecturally, overestimate security levels—and would do so in a way that varies from one cryptosystem to another. Readers not familiar with these patterns should see Appendix B for many examples.

**1.2. Formalizing and automating attack simulations.** A proof is only one way to link a model of computation, a cost metric, an attack algorithm, a cost prediction, a problem, and a success-probability prediction. Another way is to simulate the attack in that model against that problem, comparing its observed success probability (over multiple simulation runs) to the prediction, and comparing its observed cost in the model to the prediction.

Formalizing and automating this process for a list of attacks would work as follows:

- Fully specify the model of computation and a cost metric.

- Fully specify the problem under attack.

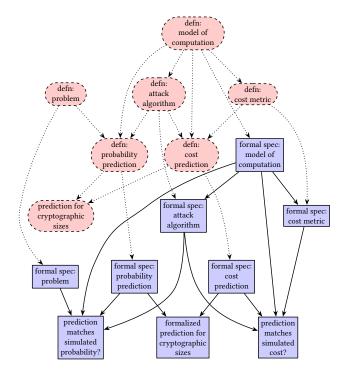

Figure 1: Data flow when an informal attack analysis (rounded dashed boxes) is supplemented with a formalization. Dotted edges are informal processes.

- Fully specify each attack algorithm in the model of computation.

- Fully specify the formula for the predicted cost of each algorithm.

- Fully specify the formula for the predicted success probability of each algorithm.

- Have a computer simulate each algorithm, comparing the observed cost to the prediction.

- Have a computer simulate each algorithm, comparing the observed success probability to the prediction.

Note that the model of computation, the cost metric, and the simulator can and should be attack-independent tools, for reusability and reviewability.

Attack simulations are already the central tool used in the literature to check conjectural attack analyses. *Formalizing* complete attack analyses would catch further errors, and would provide a clear structure for splitting reviews and risk analyses into simpler components. See Figure 1.

As examples of how attack simulations are already used, [67] tried its subset-sum algorithm, and [53] simulated its quantum Ideal-SVP algorithm. See Appendix C for how the aforementioned errors in [67] and [53] slipped past the experiments in those papers, but would have been stopped if the complete attack analyses had been formalized.

The literature sometimes presents what can be viewed as components of this type of formalization, at least for simple examples. Any software that computes predictions for cost and success probability

can be viewed as fully specifying formulas, modulo any relevant ambiguities in the programming language. The literature presents simulations checking some simple algorithms in clearly defined models of computation, and sometimes also checking cost formulas in clearly defined cost metrics. For example, [106] presents and checks a gate-level algorithm for reversible scalar multiplication, the main work inside an elliptic-curve version of Shor's algorithm.

However, this level of specification rapidly disappears as one moves to more complicated attack algorithms. It is not at all clear from the literature that it is feasible to formalize state-of-the-art cryptanalysis of unbroken cryptosystems.

**1.3.** The case of ISD. This paper focuses on one case study, called "information-set decoding" (ISD). This is the state-of-the-art attack strategy against a broad class of code-based cryptosystems, notably the well-known McEliece cryptosystem.

This paper's CryptAttackTester (CAT) software demonstrates feasibility, for this case study, of carrying out the entire linked series of formalization steps explained in Section 1.2. CAT includes formal specifications of (1) a general-purpose model of computation and cost metric, (2) the problem under attack, (3) a spectrum of ISD algorithms in this model, (4) formulas predicting the cost of each algorithm in this metric, and (5) formulas predicting the success probability of each algorithm. This paper carefully tunes the details of its ISD algorithms for performance in this metric.

CAT includes a general-purpose simulator for this model of computation. This paper reports what this simulator says about these cost and probability formulas for these ISD algorithms. In short, the cost predictions are perfect, and the success-probability predictions are close to perfect. This paper also quantifies the predicted effectiveness of these ISD algorithms for proposed McEliece parameters.

This simulator provides a clear framework for evaluating further ISD algorithms: add specifications of the algorithms and their cost/probability formulas, make sure the formulas are accurate in the simulations, and then use the formulas to compare to other algorithms. See Section 3. The framework is not limited to some preconceived notion of how ISD algorithms should be built: the same simulator can run arbitrary attack algorithms.

1.4. Reasons to take ISD as a case study. Among all proposed post-quantum public-key encryption systems, the McEliece cryptosystem has the strongest security track record. ISD was already known when the cryptosystem was introduced in 1978, and has always driven evaluations of the McEliece security level. Other known attack strategies have always been much slower than ISD, avoiding the worrisome situation of security being damaged by an improvement in any one of multiple competing lines of attack. Improvements in ISD since 1978 have made zero change in asymptotic McEliece exponents (for this asymptotic analysis see [31], [30, Section 1], and [119]), and have made only small changes in concrete exponents for security levels of interest (as Table 1 illustrates).

The fact that actual attack improvements are small is not a reason to expect analysis errors to be correspondingly small. For example, if an analysis misses an attack step, the magnitude of the error depends on how the cost of that step compares to the cost of other steps. If two different cost metrics are conflated, the magnitude of the error depends on the gap between the cost metrics. If there is a

calculation error, the magnitude of the error can be arbitrarily large. These effects have no obvious connection to how stable attacks are.

When actual security levels are converging while errors are not, it becomes more and more likely for a *claimed* algorithm improvement to be the result of an error. This confuses readers regarding security risks, and warps the scientific process of searching for better attacks.

Appendix N gives examples of the magnitude of numerical variations among estimates of ISD attack costs, especially as a result of undocumented variations in which steps are counted and how costs are assigned to those steps. This paper's formalization systematically enforces counting all steps in a clearly defined cost metric, making it much easier to see *actual* algorithm improvements.

## 2 Choosing a model of computation and a cost metric

The literature contains many different definitions of the word "algorithm", and many different definitions of cost metrics for algorithms. Often two choices are polynomially equivalent in the sense that cost C under the first definition implies cost  $C^{O(1)}$  under the second definition and vice versa, making the definitions interchangeable for, e.g., proving reductions among polynomial-time adversaries; but more precision is required when one wants to see, e.g., the difference between an attack taking time  $2^{0.5n}$ .

This section selects a particular model of computation and cost metric for this paper's case study. In short, the model is a conventional Boolean-circuit model, specifically with every  $\leq$ 2-bit-to-1-bit function allowed as a cost-1 gate. Bit 0 and bit 1 and bit copying are free. The model and metric have a simple definition (see Section 2.1) and a straightforward formalization (see Section 3.6).

Conceptually, this paper's formalization process can start with other fully defined models of computation and cost metrics. There are many possibilities in the literature beyond this particularly easy Boolean-circuit model. Appendix E summarizes other common Boolean-circuit models. Appendix F considers validation of the particular model used here. Appendix G considers the more complicated possibility of using random-access-machine models (RAM models) rather than Boolean-circuit models.

**2.1.** The selected circuit model and cost metric. The following model of computation has two parameters: nonnegative integers A and B. The model expresses algorithms as circuits that map A bits of input to B bits of output.

An **A-bit-to-***B***-bit circuit** is a sequence  $(C_A, C_{A+1}, \ldots, C_{A+L-1})$  such that (1) L is an integer with  $L \ge B$  and (2)  $C_k$ , for each  $k \in \{A, A+1, \ldots, A+L-1\}$ , has the form  $(\ell, F, i_0, \ldots, i_{\ell-1})$  where

- $\bullet \ \ell \in \{0,1,2\};$

- F is a function from  $\{0,1\}^{\ell}$  to  $\{0,1\}$ ; and

- $i_0, \ldots, i_{\ell-1} \in \{0, 1, \ldots, k-1\}.$

The **cost** of the circuit is the number of k for which  $C_k$  has the form (2, ...) or  $(1, (x \mapsto 1 - x), i)$ .

The circuit is run as follows. The input bits, in order, are labeled  $x_0, \ldots, x_{A-1}$ . The circuit computes successively  $x_A, \ldots, x_{A+L-1}$  by defining each  $x_k$  as  $F(x_{i_0}, \ldots, x_{i_{\ell-1}})$  where  $C_k = (\ell, F, i_0, \ldots, i_{\ell-1})$ . The output consists of the bits  $x_{A+L-B}, \ldots, x_{A+L-1}$  in that order.

### 3 Structure of the formalization

The output of this paper's process of formalizing ISD analyses is the CryptAttackTester (CAT) software package available from [24]. This section explains what CAT contains and how it relates to informal ISD analyses. See Appendix H for limitations in CAT.

**3.1. External interface.** The external interface of CAT consists of various functions that are automated: i.e., the software package includes software that computes these functions upon request. There are three classes of functions: *predictors*, *simulators*, and *explorers*.

The *predictors* are functions predictedcost, predictedprob, and predictedcp. Each function takes three inputs:

- A list of parameters for the problem under attack. For this ISD case study, a parameter list is a tuple (n, k, t), and the problem is to recover a secret weight-t vector  $e \in \mathbb{F}_2^n$  given a matrix  $H \in \mathbb{F}_2^{(n-k)\times n}$  and given He. See Sections 3.4 and 3.5 for how this problem is formalized.

- An attack name. For this ISD case study, attacks are named by high-level search strategies (see Section 4): isd0, isd1, and isd2. There are also straightforward bruteforce and bruteforce2 attacks as a baseline.

- A list of parameters for the attack: for example, the number of attack iterations. Each attack has its own list of parameter names

The predictedcp function outputs the predicted cost and probability of that attack, with those attack parameters, against those problem parameters. The functions predictedcost and predictedprob output cost and probability separately, saving time in some applications of predictedcp.

The *simulators* are functions circuitcost, circuitprob, and circuitexample. These take the same inputs as predicted\*, but also output the observed cost and success probability of the attack circuits for comparison to the predictions, or an input-output example for circuitexample. All of these simulators are internally built from a single unified simulator.

For example, if these functions are asked about attack=isd0 L=0 P=0 I=1 for (n,k,t)=(48,36,2), they report that the predicted circuit cost is 12325, the observed circuit cost is 12325, the predicted circuit success probability is slightly above 0.058, and the circuit was observed to succeed in 984 out of 16227 trials. The observed success probability in this example is almost 0.061; this is not a surprising deviation from the prediction for this number of trials.

If the observed success probability is outside [0.9p, 1.1p], where p is the predicted success probability, then circuitprob also returns an alert. The number of trials, 16227 in this example, is automatically chosen by circuitprob as 1000 for p > 1/2 or  $\lceil 1000(1-p)/p \rceil$  for  $p \le 1/2$ , so alerts are rare when predictions are accurate. Increasing the 1000 ("trialfactor") inside circuitprob carries out more trials; this has the disadvantage of more run time but the advantage of being able to detect smaller-scale inaccuracies in the predictions.

The *explorers* formalize various procedures for exploring the space of circuits:

problemparams generates a sequence of problem parameters to use for tests (not necessarily the full space of problem parameters). For ISD, this sequence includes examples of

- cryptographic interest such as (3488, 2720, 64) and various scaled-down examples such as (48, 36, 2).

- attackparams, given problem parameters, returns a list of pairs, where each pair consists of an attack name and an attack parameter list applicable to those problem parameters.

- searchparams uses heuristics to search for improved attack parameters, as measured by the ratio between predicted cost and predicted probability.

Note that, as in the literature, there is no guarantee that optimal attack parameters have been found (except when parameter spaces are very small). Perhaps there are large tradeoffs between the performance of an attack and the time spent finding the attack, as in the examples in [27]. The point of searchparams is to clearly specify a typical search process, not to claim that this process is optimal.

**3.2. Comparison to previous ISD analyses.** Estimates in the previous ISD literature come from "estimators" having the same basic data flow as the predictors in CAT: see, e.g., [97], [13], [55], and [57]. These estimators convert problem parameters, attack names, and attack parameters (found by search processes with varying levels of documentation) into predictions of cost and success probability.

One advantage of the predictors in CAT is that there are complete definitions of algorithms all the way down through the model of computation and cost metric, giving clear semantics to the predictions. Another advantage is that the details of the analyses of cost and probability account for various effects that the literature does not account for. Various highlights of these analyses are explained later in this paper, and the full analyses are formalized inside the predictors in CAT.

Both of these advantages follow from the central structural advantage of CAT: namely, CAT also includes a simulator, with the simulator results compared to the predictions. The simulator enforces clarity in definitions of cost metrics, and clarity in the definitions of the attacks under consideration. The comparisons provide reasons to believe that the attack analyses used the same clear cost metrics, accounted for all attack steps, and accounted for all major probability factors.

As noted in Section 1, these are not proofs. Perhaps an algorithm-analysis inaccuracy is (1) invisible in small simulations but (2) much larger at cryptographic sizes. However, this type of formalization would have rapidly caught all of the peer-reviewed errors listed in Section 1; see Appendix C for details of two examples. For the case of ISD (see Appendix N), a large underestimate in [13] would have been rapidly caught by small simulations, and smaller underestimates that this paper points out in [55] and [57] were caught by earlier stages in this paper's formalization process.

The ISD literature includes software for some slices of the space of ISD algorithms. The critical advantage of this paper's software is that it measures every attack in the same clearly defined cost metric used for cost predictions, allowing direct comparisons between measurements and predictions. For comparison, [29] includes predictions and software, but notes that "optimizing CPU cycles is different from, and more difficult than, optimizing the simplified notion of 'bit operations' " used in the predictions; [29] does not attempt to close the gap.

This paper's software also includes many more ISD algorithms than previous software. For example, Stern's algorithm [114], a specific example of isd1, was improved using random walks in [42] and more advanced random walks in [29]; but the literature has not analyzed the impact of random walks upon subsequent search strategies such as isd2. In this paper, every high-level ISD search strategy is systematically combined with the full space of random-walk strategies. As another example, this paper's collision searches systematically support tradeoffs between buffer sizes, collision-checking effort, and collision-finding probability; see the QU, PE, and WI parameters in Section 5.

**3.3.** The process of adding more attacks. Algorithm designers go beyond looking at the effectiveness of existing attacks: they consider the details of how attacks work, and search for more effective attacks. The internal structure of CAT is designed to assist in inspection of attack details and in adding further attacks to the same framework.

For example, the attack named isd2 is defined by a function named isd2. This is accompanied by an isd2\_cost function that predicts the attack cost, an isd2\_prob function that predicts the attack probability, and an isd2\_params\_valid function that defines which parameter lists are valid for this attack. There is also an isd2\_params function that generates a sequence of parameter lists for this attack; the first parameter list is the starting point for searchparams, and all parameter lists are output by attackparams.

Adding another attack and its analysis to the same framework means writing a function that constructs the circuit for the attack, along with functions for cost predictions etc., and adding these new functions to the list of attacks in CAT.

Attacks do not have to be built from scratch. Often an attack can be built as a simple modification of another attack. Many components of the attacks and analyses inside CAT are already provided as general-purpose subroutines, such as sorting to build a sorting circuit, sorting\_cost to return the cost of that circuit, and collision\_average to return a heuristic estimate for the number of collisions found by sorting two lists under a limit on the collision distance; this limit is the WI parameter in Section 5.11.

**3.4. Formalizing the problem.** A problem is formalized in CAT as a function psgen that, given a parameter list, returns a pair (P, s), where each of P and s is a bit vector of length determined by the parameter list. A problem is also accompanied by functions params (used inside problemparams) and num{inputs, outputs} (which are used as explained in Appendix K).

A trial in circuitprob, for any particular problem and any particular attack circuit, uses psgen to generate a pair (P, s), and asks whether input P to the circuit produces output s. Informally, the problem is to find the "secret" information s given the "public" information s.

This class of problems includes, for example, the one-wayness ("OW-CPA") problem for any public-key-encryption system (PKE) equipped with bit-vector encodings. In the OW-CPA problem, a public key is generated as specified by the PKE; a plaintext is chosen uniformly at random from the plaintext space; a ciphertext is obtained by encrypting the plaintext under that public key; the attacker's goal is to recover the plaintext, given the public key and the ciphertext. This fits straightforwardly into CAT, with the public

bit vector P encoding the public key and the ciphertext, and the secret bit vector s encoding the plaintext.

For interesting problems, psgen is randomized, so there are many choices of (P,s). Currently randomness comes from a DRBG with known seeds for reproducibility. The DRBG is the mt19937\_64 DRBG built into the C++ programming language, not a DRBG designed to be cryptographically strong. The DRBG is isolated inside a small random module in CAT so that it can be easily replaced. Preliminary experiments with other DRBGs have not detected any influence of the DRBG choice upon any of the attacks in CAT. It would also be possible to run simulations using a hardware RNG.

**3.5.** An example of a problem. The uniformmatrix problem in CAT has integer parameters (n,k,t) where  $n\geq 8$ ;  $0.7n\leq k\leq 0.8n$ ; and  $k=n-t\lceil\log_2 n\rceil$ . The secret information is an n-bit vector  $e\in\mathbb{F}_2^n$  generated uniformly at random subject to the constraint of having Hamming weight t. The public information is a uniform random matrix  $T\in\mathbb{F}_2^{(n-k)\times k}$  and a ciphertext He, where  $H\in\mathbb{F}_2^{(n-k)\times n}$  is defined as an identity matrix followed by T. This problem has the virtue of simplicity, and the virtue of match-

This problem has the virtue of simplicity, and the virtue of matching what is considered in typical ISD analyses. This problem is identical to the OW-CPA problem for a PKE where key generation returns public key *T* and an empty secret key; encryption of plaintext *e* produces ciphertext *He*; and decryption always fails. Decryption does not appear in the OW-CPA definition and is not used in CAT.

For small parameters, public keys in this PKE are easily distinguishable from public keys in the McEliece PKE (which uses a key-generation procedure different from this PKE and a decryption procedure different from this PKE), and in particular plaintexts often collide under encryption in this PKE while they never do in the McEliece PKE. Appendix K analyzes how these collisions reduce attack success probabilities. For large parameters, all known methods of distinguishing the two PKEs are much slower than known OW-CPA attacks; see generally [8].

The choice of putting an identity matrix before T matches [8]. Internally, the attacks in CAT rearrange input columns (at cost 0) to put the identity matrix after T, and rearrange output bits accordingly (also at cost 0). This makes some attack steps slightly easier to describe.

Structurally, CAT is not limited to the uniformmatrix problem. See Appendix I for another problem already included in CAT, an AES-128 key-search problem.

**3.6. Formalizing the model of computation.** Informally, each attack is an algorithm that, given problem parameters and attack parameters, constructs a circuit as in Section 2.1. The circuit is applied to a problem instance to produce an output. The algorithm that generates a circuit is called a "meta-circuit" in the following paragraphs, to avoid confusion with the algorithm expressed by the circuit per se.

The meta-circuit is formalized as a function in C++. The function arguments are problem parameters, attack parameters, and a problem instance. The problem instance consists of a bit vector (P above) of length determined by the parameters. Each bit uses a bit class defined centrally by bit.h. The function returns an output,

namely a vector of bit values, where again the vector length is determined by the parameters.

To construct a circuit, the meta-circuit simply carries out operations on bit values; bit.h automatically tracks the circuit cost. For example, one of the lowest-level subroutines is a half\_adder subroutine that adds two bits a and b to obtain a two-bit sum, namely a bottom bit s and a carry bit c. The code for the subroutine says  $s = a \land b$  and c = a & b.

The usual C/C++ notation is supported for AND (&), OR (|), XOR (^), and NOT (~); the half\_adder example used this notation for XOR and AND. All 2-bit operations are supported with conventional gate names such as a.andn(b). Constructing bit(0) and bit(1) is free, as is copying.

(Section 2.1 also allows uninteresting cost-1 2-input gates that output 0, 1, or a copy of an input. For completeness of the formalization of the model, note that these gates can be computed as bit(0)&bit(0), bit(1)&bit(1), or b&b respectively.)

As another low-level example, there is a bit\_vector\_ixor function that XORs a vector w into a vector v:

Here .at(i) is bounds-checked C++ array access, which is used systematically throughout CAT to avoid the well-known risk of accidents from non-bounds-checked [i]. (Protection against accidents should not be confused with protection against malice: adding malicious attack code to CAT can exploit the known DRBG seeds, overwrite results, destroy files, etc.)

CAT provides an abstract integer type, bigint, to shield formalizations from the limited-size "integral" types in C++ (and from the resulting ambiguities: the size limits are compiler-dependent). Internally, CAT implements bigint via GMP, and GMP's overhead creates a considerable circuit\* slowdown, presumably increasing the risk that prediction errors will be missed. It is not easy to compare this risk to the risk of error arising from using, e.g., a 64-bit integral type for inner loops. It is well known that languages can in principle make bigint much faster, with multiple code paths and range analysis to automatically replace bigint with a fast fixed-width type in most cases, but so far this has received less compiler support than analogous hoisting of bounds checks.

Meta-circuits do not inspect the values of the bits that they are operating upon, so the circuits that they build are independent of the inputs, as in the informal description of an attack. The probability simulator circuitprob automatically runs circuits on many inputs at once in bitsliced form.

#### 4 ISD variants

This section and Section 5 describe the attacks covered in CAT against the problem defined in Section 3.5. This section emphasizes the central mathematical objects computed in these ISD variants. Section 5 emphasizes the construction and optimization of circuits for subroutines to compute those objects.

See Section 6 for examples of choosing ISD variants to attack specific problem sizes. These choices depend on costs and success probabilities for the complete ISD circuits, including the layers in this section and in Section 5. A closer look at the details shows interactions across layers: for example, understanding the cost of linear-algebra circuits is important for seeing the benefit of the new random-walk parameter *Y* introduced below. These choices are also influenced by the model of computation and cost metric: for example, the literature already indicates that accounting for two-dimensional or three-dimensional communication costs tends to favor fewer levels of collision search and a smaller *p* parameter.

**4.1. Relationship to the literature.** Before presenting the attacks, this section summarizes how these attacks relate to previous work.

After Prange's original ISD algorithm in 1962 [102], ISD variants developed in two major directions. One direction is improvements in linear-algebra costs; this includes random walks through information sets (credited in [46] to Omura), combinatorial searches to reuse linear algebra for many tests (Lee–Brickell [75]), and testing only a limited number of bits (Leon [80]).

Omura's random walks changed one position in an information set to obtain a new information set. Canteaut–Chabaud [41] and Canteaut–Sendrier [42] considered an analogous modification of Stern's algorithm, and used Markov chains to analyze the impact. Bernstein–Lange–Peters [29] showed that changing multiple positions at a time further improves Stern's algorithm, at the expense of a more complicated Markov-chain analysis.

The other major direction is asymptotically better combinatorial searches, including 1 level of collision search (as in Stern [114] and Dumer [54]), 2 levels of collision search (as in May–Meurer–Thomae [82], which adapted Howgrave-Graham–Joux [67] to decoding), and allowing collisions with partial cancellations (as in Becker–Joux–May–Meurer [18], which adapted Becker–Coron–Joux [15] to decoding).

The attacks and analyses in CAT systematically integrate random walks with 0, 1, or 2 levels of collision search. The attack description below first explains the random walks, and then explains the three search options. For 2 levels, collisions with partial cancellations are supported in CAT, and the analysis of the "C=1" option described below appears to be new. Some search techniques that the literature describes as small improvements are not included in CAT: ball-collision decoding as in [30], 3 levels of collision search as in [18], and nearest-neighbor search as in [83].

The random walks in CAT are more general than the random walks in [29]. The *X* parameter in this paper is the number of positions changed, matching the "c" parameter in [29]; the new *Y* parameter in this paper reduces the number of positions considered for a change. Taking the maximum possible choice of *Y* matches the random walks in [29]. Taking much smaller *Y* creates a noticeable chance of a failed information-set update spoiling all

$<sup>^2</sup>An$  experiment that modified CAT to instead use long long for vector indices in meta-circuits reduced the time for CAT's isdsims.py script (see Section 6) by an order of magnitude and produced the same output.

<sup>&</sup>lt;sup>3</sup>Faster simulations allow a larger limit on the simulation size that the user can afford for any given amount of CPU time spent on simulations. Perhaps this larger limit makes a prediction error visible. See generally Appendix L.

subsequent iterations, but periodic **resets** in this paper limit the impact of failures: a completely new information set is chosen every RE iterations, starting from the original input matrix, producing a new **chain** of information sets. Manual parameter selection would take RE large enough to hide the occasional reset costs compared to per-iteration search costs, and would take Y somewhat above  $X + \log_2 RE$  so that it is rare for a chain to fail.

**4.2. Notation.** By  $I \oplus J$ , we denote the symmetric difference of two sets I and J. Given a nonnegative integer d, we denote by [d] the set  $\{0, 1, \ldots, d\}$ . Vectors, if not stated otherwise, are considered as column vectors over  $\mathbb{F}_2$ . By  $v \mid v'$ , we denote the result of concatenating vectors v and v'. By wt(v) we denote the Hamming weight of a vector v. By  $v_i$  we denote entry i (the index starts from 0) of a vector v. We denote by  $u_i$  the ith unit vector, of which the length depends on the context. We denote by v0 the vector v1 in  $\mathbb{F}_2^d$  such that  $v_i = 1$  if and only if  $i \in I$ 1. By v1 and v2 we denote the number of rows of a matrix v3. By v4. By v5 we denote the number of columns of a matrix v6. By v7 we denote row v8 a matrix v8 denote column v9 denote column v9 a matrix v9. Similarly, by v1, where v9 is a set of integers, we denote v9 in v9. Given an integer v9, we denote by v9 denote by v9 denote by v9 denote by v9. We denote by v9 denote by v9 denote by v9. We denote by v9 denote by v9. We denote by v9 denote by v

$$\Big\{ \big( s + A[I], I \big) \mid I \subseteq \big[ \operatorname{ncols}(A) - 1 \big], |I| = d \Big\}.$$

Similarly, we denote by  $S_d(A, A', s, s')$  the set

$$\Big\{ \big(s+A[I],s'+A'[I],I\big) \mid I \subseteq \big[\operatorname{ncols}(A)-1\big], |I|=d \Big\}.$$

**4.3. Attack overview.** Each attack takes two inputs  $H \in \mathbb{F}_2^{(n-k) \times n}$  and  $s \in \mathbb{F}_2^{n-k}$  and outputs a vector  $e \in \mathbb{F}_2^n$ , where the last n-k columns of H form an identity matrix (i.e., H is in **systematic form**). Each attack tries to ensure that e is a vector of Hamming weight t satisfying He = s.

(Note that the problem in Section 3.4 is different. The identity matrix there is at a different position, and success in the OW-CPA problem requires recovering a particular preimage of s under H, which is a narrower notion than finding an arbitrary preimage when there are multiple preimages. See Appendix K.)

Each attack consists of a sequence of **iterations** followed by a simple **post-processing phase**. The number of iterations is specified by a parameter IT > 0. Each iteration consists of two phases: a **column-permutation phase** and a **search phase**. The column-permutation, search, and post-processing phases are described below.

Each attack has a parameter  $FW \in \{0,1\}$ . If FW = 1 then the attack begins by extending H to include a row  $(1,1,\ldots,1)$ , extending s to include a corresponding bit t mod 2, reducing the new H to systematic form (and failing if this reduction fails), adjusting s accordingly, and reducing k to k-1. For literature using the known sum of elements of e to reduce k by 1, see [48, page 57, "zero mean"] for lattices, [49, full version, Section 6.3] for lattices, and [57, Section 3.1] for codes.

**4.4. Column-permutation phase.** Each column-permutation phase applies in-place operations to a matrix  $\tilde{H}$  and a vector  $\tilde{s}$ , where  $\tilde{H}$  and  $\tilde{s}$  are scrambled versions of H and s, respectively. The

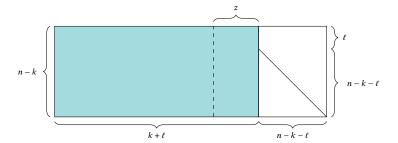

Figure 2: A  $(n-k) \times n$  matrix in generalized systematic form.

operations applied to  $\tilde{s}$  are simply the same as the row operations that are applied to  $\tilde{H}$ , so below we only talk about operations that are applied to  $\tilde{H}$ . The column-permutation phase uses four attack parameters:  $\ell \geq 0$ , RE > 0, X > 0, and  $Y \geq X$ .

By definition, a matrix A is in **generalized systematic form** if the last  $\operatorname{nrows}(A) - \ell$  columns of the matrix consist of  $\ell$  zero rows and an identity matrix. Figure 2 depicts an  $(n-k) \times n$  matrix in generalized systematic form. (This form is also used in previous papers such as [82], usually without a name.) Each column-permutation phase aims to permute the columns of  $\tilde{H}$  in a sufficiently random way while keeping  $\tilde{H}$  in generalized systematic form.

The operations carried out in a column-permutation phase depend on the iteration number, as described below.

- **4.4.1. First iteration.** If the iteration number is 0, the column-permutation phase first sets two variables  $\tilde{H}$  and  $\tilde{s}$  to H and s, respectively. Then, for each  $i \in \{0,\dots,\ell-1\}$  in order,  $b_{i,j}\tilde{H}_i$  is added to  $\tilde{H}_j$  for each  $j \neq i$ , where each  $b_{i,j} \in \mathbb{F}_2$  is chosen randomly. (Without the row additions, almost all entries in  $\tilde{H}[k],\dots,\tilde{H}[k+\ell-1]$  would be 0, which in experiments produces considerable deviations from the predicted success probability.)

- **4.4.2. Starting a subsequent chain.** If the iteration number is a non-zero multiple of RE, the column-permutation phase sets  $\tilde{H}$  and  $\tilde{s}$  to H and s, respectively. Then, the column-permutation phase permutes the columns of  $\tilde{H}$  randomly, reduces  $\tilde{H}$  to row-echelon form, and permutes the columns of  $\tilde{H}$  to bring it to systematic form. Finally, each of the first  $\ell$  rows is added to other rows in a random way, as in the first iteration.

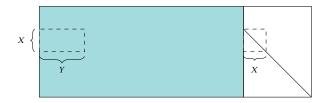

- **4.4.3. Inside a chain.** If the iteration number is not a multiple of RE, the column-permutation phase consists of three steps. These steps are designed to save bit operations by permuting only a small set of columns of  $\tilde{H}$  instead of all columns. See Figure 3.

The first step applies a random permutation to the first  $k+\ell$  columns of  $\tilde{H}$ . It then applies another random permutation to the last  $n-k-\ell$  columns of  $\tilde{H}$ , and the same permutation to the last  $n-k-\ell$  rows of  $\tilde{H}$ .

The second step applies row operations to rows  $\tilde{H}_{\ell},\ldots,\tilde{H}_{\ell+X-1}$  so that the  $X\times Y$  submatrix formed by the first Y columns of the resulting rows is in reduced row-echelon form. It then permutes the columns  $\tilde{H}[0],\ldots,\tilde{H}[Y-1]$  and  $\tilde{H}[k+\ell],\ldots,\tilde{H}[k+\ell+X-1]$  so that the intersection between  $\tilde{H}_{\ell},\ldots,\tilde{H}_{\ell+X-1}$  and  $\tilde{H}[k+\ell],\ldots,\tilde{H}[k+\ell]$

Figure 3: The attack parameters X and Y.

$\ell + X - 1$ ] becomes an identity matrix. It then uses row operations to bring  $\tilde{H}$  to generalized systematic form.

The third step works in the same way as the first step, making new choices of random permutations.

Ensuring that all X columns are exchanged with new columns is the "type 3" approach described in [29, "Analysis of the number of iterations"]. Considering only Y choices of new columns allows a smaller column-permutation circuit.

**4.5. Search and post-processing phases.** After each column-permutation phase, there is a permutation matrix P and an invertible matrix A such that

$$\tilde{H} = AHP, \ \tilde{s} = As.$$

Consequently, given P and any weight-t vector  $\tilde{e}$  that satisfies  $\tilde{H}\tilde{e} = \tilde{s}$ , it is easy to compute a weight-t vector  $e = P\tilde{e}$  such that  $He = HP\tilde{e} = s$ . The goal of each search phase is to find such  $\tilde{e}$  given  $\tilde{H}$  and  $\tilde{s}$ , while the goal of the post-processing phase is to derive  $e = P\tilde{e}$ .

The matrix P is represented as a vector  $\pi = (\pi_0, \ldots, \pi_{n-1}) \in \mathbb{Z}^n$  where  $P[i] = u_{\pi_i}$ . Whenever  $\tilde{H}$  is set to H (inside the first iteration of each chain),  $\pi$  is set to  $(0, 1, \ldots, n-1)$ ; whenever a column permutation is applied to  $\tilde{H}$ , the same permutation is applied to entries of  $\pi$ . Whenever a solution for  $\tilde{e}$  is found in a search phase,  $\pi$  is stored into a **solution buffer**, along with some data from which  $\tilde{e}$  can be derived. The post-processing phase derives  $\tilde{e}$  from the data in the solution buffer and computes e as  $P\tilde{e}$ .

Three options for the search phase are described below: isd0, isd1, and isd2. The reader may wish to interpret each " $S \cdots \subseteq \cdots$ " below as " $S \cdots = \cdots$ " for an initial understanding of the attacks, but optimizing the new QU, PE, and WI parameters in Section 5 usually produces smaller subsets.

- **4.6.** Failure to maintain generalized systematic form. Updates to the solution buffer are controlled by an update-permitted bit. If the  $X \times Y$  matrix from which the column-permutation phase computes reduced row-echelon form is not full rank then the column-permutation phase fails to bring  $\tilde{H}$  to generalized systematic form. The column-permutation phase then clears the update-permitted bit. Each new chain sets the update-permitted bit to 1.

- **4.7. isd0: 0 levels of collision search.** The following text describes the search phase in CAT's isd0 attack. There are three attack parameters that matter for the search, called p,  $\ell$ , and z. This attack includes, for example, Prange's original ISD algorithm (parameters p=0 and  $\ell=0$ ), the Lee–Brickell algorithm (p>0 and  $\ell=0$ ), and Leon's algorithm ( $\ell>0$ ).

The first  $k + \ell - z$  columns of  $\tilde{H}$  are viewed as

$$\begin{pmatrix} T^{(0)} \\ T^{(1)} \end{pmatrix} \in \mathbb{F}_2^{(n-k)\times(k+\ell-z)},$$

where  $\operatorname{nrows}(T^{(0)}) = \ell$  and  $\operatorname{nrows}(T^{(1)}) = n - k - \ell$ . Similarly,  $\tilde{s}$  is considered as  $\tilde{s}^{(0)} \mid\mid \tilde{s}^{(1)}$ , where  $\tilde{s}^{(0)} \in \mathbb{F}_2^{\ell}$  and  $\tilde{s}^{(1)} \in \mathbb{F}_2^{n-k-\ell}$ .

In the case  $\ell > 0$ , each search phase first computes

$$S^{(1)} \subseteq \left\{ I \mid (0, I) \in \mathcal{S}_p(T^{(0)}, \tilde{s}^{(0)}) \right\}.$$

Then, for each  $I \in S^{(1)}$ , the search phase computes  $v = \tilde{s}^{(1)} - T^{(1)}[I]$  and checks if wt(v) = t - p.

In the case  $\ell = 0$ , for each (v, I) in  $S_p(T, \tilde{s})$ , the search phase checks if  $\operatorname{wt}(v) = t - p$ . Here T is the first k - z columns of  $\tilde{H}$ .

Either way, if the check passes, then  $\tilde{H}\tilde{e}=\tilde{s}$  must hold for the weight-t vector

$$\tilde{e} = (\text{vec}(I, k + \ell - z) \mid\mid (0, ..., 0) \mid\mid v) \in \mathbb{F}_2^n$$

The search phase then stores I and v in the solution buffer, so that the post-processing phase can derive  $\tilde{e}$ .

**4.8. isd1: 1 level of collision search.** CAT's isd1 attack again has three attack parameters that matter for the search, called p',  $\ell$ , and z. This attack includes, e.g., Stern's algorithm (with  $z = \ell$ ) and Dumer's algorithm (with z = 0). The parameters p' and  $\ell$  are required to be positive. The parameter p' in isd1 is analogous to p in isd0 in how it controls list sizes, but isd1 uses these lists to search for 2p' errors while isd0 uses these lists to search for p errors.

The search phase in isd1 works as follows. Matrices  $T^{(0)}$ ,  $T^{(1)}$  and vectors  $\tilde{s}^{(0)}$ ,  $\tilde{s}^{(1)}$  are defined in the same way as in isd0, and we consider

$$T^{(i)} = \begin{pmatrix} T_L^{(i)} & T_R^{(i)} \end{pmatrix},$$

where  $\operatorname{ncols}(T_L^{(i)}) = \lfloor (k+\ell-z)/2 \rfloor$  and  $\operatorname{ncols}(T_R^{(i)}) = \lceil (k+\ell-z)/2 \rceil$ .

Each search phase first computes two sets

$$S_L = S_{p'}(T_L^{(0)}, 0), S_R = S_{p'}(T_R^{(0)}, \tilde{s}^{(0)}).$$

Then a collision search between  $S_L$  and  $S_R$  is carried out to find

$$S^{(1)} \subseteq \left\{ (I_L, I_R) \mid (v, I_L) \in S_L \text{ and } (v, I_R) \in S_R \text{ for some } v \right\}.$$

For each  $(I_L,I_R)\in S^{(1)}$ , the search phase computes  $w=\tilde{s}^{(1)}-(T_L^{(1)}[I_L]+T_R^{(1)}[I_R])$  and checks if  $\operatorname{wt}(w)=t-2p'$ . If so,  $\tilde{H}\tilde{e}=\tilde{s}$  must hold for the weight-t vector

$$\tilde{e} = (\operatorname{vec}(I_L, \lfloor k+\ell-z)/2 \rfloor) \mid |\operatorname{vec}(I_R, \lceil k+\ell-z)/2 \rceil) \mid |(0, \dots, 0)| \mid w)$$

in  $\mathbb{F}_2^n$ . The search phase then stores  $I_L$ ,  $I_R$ , w in the solution buffer, so that the post-processing phase can derive  $\tilde{e}$ .

**4.9. isd2: 2 levels of collision search.** Attack parameters in CAT's isd2 attack include  $\ell_0 > 0$  and  $\ell_1 > 0$ , with  $\ell$  defined as  $\ell_0 + \ell_1$ ;  $z; p'' > 0; p' \in \{0, 2, \dots, 2p''\}; C \in \{0, 1\};$  and  $D \in \{1, \dots, 2^{\ell_0}\}.$  The case C = 0 with p' = 2p'' is due to 2011 May–Meurer–

The case C = 0 with p' = 2p'' is due to 2011 May–Meurer–Thomae [82] (MMT). The case C = 0 with p' < 2p'' is due to 2012 Becker–Joux–May–Meurer [18] (BJMM). The case C = 1 ignores p' and is essentially [63, Table 3], but the analysis in [63] treats this algorithm as succeeding only when the MMT algorithm does,

whereas the CAT analysis accounts for further success cases in the algorithm.

The first  $k + \ell - z$  columns of  $\tilde{H}$  are viewed as

$$\begin{pmatrix} T^{(0)} \\ T^{(1)} \\ T^{(2)} \end{pmatrix} \in \mathbb{F}_2^{(n-k)\times(k+\ell-z)},$$

where  $\operatorname{nrows}(T^{(0)}) = \ell_0$ ,  $\operatorname{nrows}(T^{(1)}) = \ell_1$ , and  $\operatorname{nrows}(T^{(2)}) = n - k - \ell$ . Similarly,  $\tilde{s}$  is considered as  $\tilde{s}^{(0)} \mid\mid \tilde{s}^{(1)} \mid\mid \tilde{s}^{(2)}$ , where  $\tilde{s}^{(0)} \in \mathbb{F}_2^{\ell_0}$ ,  $\tilde{s}^{(1)} \in \mathbb{F}_2^{\ell_1}$ ,  $\tilde{s}^{(2)} \in \mathbb{F}_2^{n-k-\ell}$ . We further consider

$$T^{(i)} = \begin{pmatrix} T_I^{(i)} & T_R^{(i)} \end{pmatrix},$$

where  $\operatorname{ncols}(T_L^{(i)}) = \lfloor (k+\ell-z)/2 \rfloor$  and  $\operatorname{ncols}(T_R^{(i)}) = \lceil (k+\ell-z)/2 \rceil$ , respectively.

The attack parameter D is used to specify the size of a set  $S_{\Delta} \subseteq \mathbb{F}_{2}^{l_{0}}$ . For each  $\Delta \in S_{\Delta}$ , each search phase first computes

$$\begin{split} S_L^{(0)} &= \mathcal{S}_{p''}(T_L^{(0)}, T_L^{(1)}, 0, 0), \\ S_R^{(0)} &= \mathcal{S}_{p''}(T_R^{(0)}, T_R^{(1)}, \Delta, 0), \\ \hat{S}_R^{(0)} &= \mathcal{S}_{p''}(T_R^{(0)}, T_R^{(1)}, \tilde{s}^{(0)} + \Delta, \tilde{s}^{(1)}). \end{split}$$

Then, a collision search between  $S_L^{(0)}$  and  $S_R^{(0)}$  is performed to build

$$S^{(1)} \subseteq \left\{ (w_L + w_R, I_L, I_R) \mid (v, w_L, I_L) \in S_L^{(0)}, (v, w_R, I_R) \in S_R^{(0)} \right\}.$$

Similarly, a collision search between  $S_L^{(0)}$  and  $\hat{S}_R^{(0)}$  is performed to build

$$\hat{S}^{(1)} \subseteq \left\{ (\hat{w}_L + \hat{w}_R, \hat{I}_L, \hat{I}_R) \mid (v, \hat{w}_L, \hat{I}_L) \in S_L^{(0)}, (v, \hat{w}_R, \hat{I}_R) \in \hat{S}_R^{(0)} \right\}.$$

Once  $S^{(1)}$  and  $\hat{S}^{(1)}$  are obtained, another collision search is performed to build

$$S^{(2)} \subseteq \left\{ (I_L, \hat{I}_L, I_R, \hat{I}_R) \mid (v, I_L, I_R) \in S^{(1)}, (v, \hat{I}_L, \hat{I}_R) \in \hat{S}^{(1)} \right\}$$

if C = 1. If C = 0,  $S^{(2)}$  is built in a similar way except that each  $(I_L, \hat{I}_L, I_R, \hat{I}_R) \in S^{(2)}$  needs to satisfy two additional constraints  $|I_L \oplus \hat{I}_L| = p'$  and  $|I_R \oplus \hat{I}_R| = p'$ .

$|I_L \oplus \hat{I}_L| = p'$  and  $|I_R \oplus \hat{I}_R| = p'$ . Once  $S^{(2)}$  is obtained, for each  $(I_L, \hat{I}_L, I_R, \hat{I}_R) \in S^{(2)}$ , the search phase then computes  $w = \tilde{s}^{(2)} - (T_L^{(2)}[I_L \oplus \hat{I}_L] + T_R^{(2)}[I_R \oplus \hat{I}_R])$  and checks

- in the case C = 0: whether wt(w) = t 2p';

- in the case C = 1: whether  $|I_L \oplus \hat{I}_L| + |I_R \oplus \hat{I}_R| + \text{wt}(w) = t$ .

If so,  $\tilde{H}\tilde{e} = \tilde{s}$  holds for the weight-t vector

$$\tilde{e} = (\operatorname{vec}(I_L \oplus \hat{I}_L, \lfloor k+\ell-z \rfloor) || \operatorname{vec}(I_R \oplus \hat{I}_R, \lceil k+\ell-z \rceil) || (0, \dots, 0) || w)$$

in  $\mathbb{F}_2^n$ . The search phase then stores  $I_L$ ,  $\hat{I}_L$ ,  $I_R$ ,  $\hat{I}_R$ , w in the solution buffer so that the post-processing phase can derive  $\tilde{e}$ .

### 5 Circuits for the ISD variants

This section explains how the circuits in CAT handle the subroutines needed for Section 4: reducing matrices to echelon form, finding collisions, etc.

There are many improvements here compared to naive circuit designs. Some of the improvements show how ISD subroutines can exploit known techniques such as fast sorting networks. Some of the improvements provide new tradeoffs between cost and success probability for ISD subroutines: for example, taking this section's WI parameter to be small accelerates collision-finding at the expense of sometimes missing collisions, a tradeoff that turns out to be worthwhile.

- **5.1. Queues.** An important low-level tool is a fixed-length queue of fixed-size vectors. Conditionally pushing a vector into a queue, given a bit c, means pushing the vector into the queue if c=1, and not doing anything if c=0. To carry out this operation, first conditionally move each vector in the queue except for the last one to the next vector, and then conditionally move the new vector to the first vector. To conditionally move variable  $b_0 \in \mathbb{F}_2$  to variable  $b_1 \in \mathbb{F}_2$  given the condition bit  $c \in \mathbb{F}_2$ , simply overwrite  $b_1$  with  $b_1 + c(b_0 + b_1)$  ("MUX"), at cost 3. In other words, if the queue consists of q vectors each of d bits, conditionally pushing a new vector into the queue costs 3dq.

- **5.2.** Hamming-weight computation. Let  $v \in \mathbb{F}_2^d$ . Computing  $\operatorname{wt}(v)$  costs 0 if d=1 and costs 2 (half\_adder) if d=2. For  $d\geq 3$ , CAT uses the algorithm described in [36], which works as follows. Let  $\alpha$  be the largest integer such that  $\alpha+1\leq d$  and  $\alpha+1$  is power of 2. Let  $\beta=d-1-\alpha$ . The algorithm recursively computes  $w_\alpha$  and  $w_\beta$ , the Hamming weights of the first  $\alpha$  coordinates and the next  $\beta$  coordinates of v, respectively. Finally,  $\operatorname{wt}(v)$  is computed as  $w_\alpha+w_\beta+v_{d-1}$ , in a way that  $v_{d-1}$  serves as the carry-in bit.

- **5.3.** Computing  $S_d(A, v)$ . CAT computes  $S_d(A, v)$  by computing the leaves of a tree. Each node in the tree is of the form  $\mathcal{N}(v, A, I) := (v + A[I], I)$ , where  $I \subseteq [\operatorname{ncols}(A) 1]$  and  $|I| \le d$ . The root of the tree is defined as  $\mathcal{N}(v, A, \emptyset)$ . The children of the root are defined as

$$\mathcal{N}(v, A, \{d-1\}), \dots, \mathcal{N}(v, A, \{\text{ncols}(A) - 1\}).$$

The children of a node  $\mathcal{N}(v, A, I)$  with 0 < |I| < d are defined as

$$\mathcal{N}(v, A, I \cup \{d - |I| - 1\}), \dots, \mathcal{N}(v, A, I \cup \{\min(I) - 1\}).$$

A node  $\mathcal{N}(v,A,I)$  is considered as a leaf node if |I|=d. The leaf nodes form  $\mathcal{S}_d(A,v)$ . CAT computes each non-root node from its parent using exactly 1 vector addition. In this way, under the condition that  $d \leq 10$  and  $100 \leq \operatorname{ncols}(A) \leq 10000$ , on average it takes no more than 1.11 vector additions to compute each element in  $\mathcal{S}_d(A,v)$ .

**5.4. Random-access memory (RAM) operations.** Sometimes CAT needs to compute A[i] given a matrix A and an index i, where i depends on the entries in H and s. Similarly, sometimes CAT need to set A[i] to v given a matrix A, an index i, and a vector v. The circuits for these **RAM read** and **RAM write** operations imitate real-world RAM circuits. For example, each RAM read operation is carried out by computing the root of a binary tree, where the columns of A form the leaves. Each non-leaf node with left child x and right child y is of value (1-b)x+by, where b is a specific bit in i: b is the least significant bit of i if the node is in the second lowest level of the tree, and b is the second least significant bit if the node is in the third lowest level of the tree, and so on. The value of each node with only 1 child is same as that of the child.

**5.5. Sorting.** Knuth's "merge exchange" algorithm [70] sorts a list L of d elements using  $\Theta(d \log^2 d)$  compare-and-exchange operations, with small hidden constants, and is used for sorting in CAT. (Other algorithms are known using  $\Theta(d \log d)$  compare-and-exchange operations, but with much larger  $\Theta$  constants.) Each compare-and-exchange operation exchanges L[i] and L[j] if L[i] > L[j], for some i, j such that i < j.

Sorting is used for various operations, in particular for collision search. See Section 5.11 for more details on collision search.

- **5.6.** Computing the sum of specific columns. Often CAT needs to compute A[I] for a matrix A and a set of indices I. It uses one of two approaches to compute A[I]. The first one is to simply obtain the corresponding columns by carrying out |I| RAM reads and then compute the sum of the columns. The second one is to first compute vec(I, ncols(A)) via sorting and then multiply by A. For any given input size, CAT automatically predicts the cost of both approaches and selects the lower-cost approach.

- **5.7.** Computing the size of symmetric difference. One of the operations required in isd2 is computation of  $|I \oplus J|$ , where each of I and J is a set of p'' indices. Here CAT first sorts the indices in I and J together to form a sorted list L of length 2p'' and sets a variable v to  $(1, \ldots, 1) \in \mathbb{F}_2^{2p''}$ . Then, for  $i = 0, \ldots, 2p'' 2$ , if  $v_i = v_{i+1} = 1$  and L[i] = L[i+1],  $v_i$  and  $v_{i+1}$  are both set to 0. Finally,  $|I \oplus J|$  is obtained as  $\operatorname{wt}(v)$ .

- **5.8. Computing reduced row-echelon form.** To compute reduced row-echelon form of a matrix  $A \in \mathbb{F}_2^{a \times b}$  where  $a \leq b$ , CAT uses the following algorithm from [45]:

- (1) Set r = 0.

- (2) Set v to the logical OR of  $A_r, \ldots, A_{a-1}$ .

- (3) Find the index j of the first nonzero entry in v. If v = 0, set j to any value in  $\{0, \ldots, b-1\}$ .

- (4) For  $i \in \{r+1, \dots a-1\}, A_r \leftarrow A_r + A_i \cdot (1 A_{r,i}).$

- (5) For  $i \in \{0, ..., a-1\} \setminus \{r\}, A_i \leftarrow A_i + A_r \cdot A_{i,j}$ .

- (6) If r + 1 < a, increase r by 1 and go back to Step 2.

Unrolling eliminates r, so Steps 1 and 6 cost 0. Step 2 is carried out using (a-r-1)b ORs. Step 4 and 5 are carried out using RAM operations: since j is known only after Step 3, RAM operations are used to read  $A_{r,j}$  from  $A_r$  and read  $A_{i,j}$  from  $A_i$ . A minor optimization mentioned in [45], and used in CAT, is to make Steps 2, 3, 4, 5 only work on entries in  $A[r], \ldots, A[b-1]$ .

In Step 3, it is required to find the index j of the first 1 in a vector of length b. If b=1, j is simply set to 0. Now assume  $b\geq 2$ . Let  $\alpha$  be the integer such that  $2^{\alpha} < b$  and  $2^{\alpha+1} \geq b$ . Note that j can be represented as a vector of  $\alpha+1$  bits. To compute j, CAT carries out the following steps for  $i=\alpha,\ldots,0$ :

- (1) Compute  $j_i$  as  $(1 v_0) \cdots (1 v_{2^i 1})$ .

- (2) For all d such that  $d < 2^i$  and  $d + 2^i < b$ , conditionally move  $v_{d+2^i}$  to  $v_d$  by considering  $j_i$  as the condition bit.

Note that if v = 0, we might have  $j \ge b$  after the 3 steps are carried out. The circuits still compute reduced row-echelon form correctly

in this case because RAM reads ensure that an entry of  $A_r$  or  $A_i$  will be obtained even when  $j \ge b$ .

**5.9. Permuting columns.** In each column-permutation phase, it is required to permute some columns of  $\tilde{H}$  in a random way. Each circuit permutes the columns in a deterministic way, which is chosen randomly from all possible ways to permute the columns when the circuit is generated. This is simply copying data, at cost 0. (The wiring used here would be visible in a cost metric that accounts for communication costs.)

When the iteration number is a nonzero multiple of RE, the random column permutation is followed by a reduction to row-echelon form, and then by a conversion to systematic form, which works as follows. Let the column indices of the pivots be  $i_0,\ldots,i_{n-k-1}$ , where  $i_0 < i_1 < \cdots < i_{n-k-1}$ . To bring  $\tilde{H}$  to systematic form, simply swap  $\tilde{H}[i_{n-k-1}]$  with  $\tilde{H}[n-1]$ , swap  $\tilde{H}[i_{n-k-2}]$  with  $\tilde{H}[n-2]$ , and so on, using n-k RAM reads and n-k RAM writes. Similarly, when the iteration number is not a multiple of RE, CAT carries out X RAM reads and X RAM writes to permute  $\tilde{H}[0],\ldots,\tilde{H}[Y-1]$  and  $\tilde{H}[k+\ell],\ldots,\tilde{H}[k+\ell+X-1]$ .

**5.10. Search phase in isd0.** Denote by  $\mathcal{E}(c)$  a bit which is of value 1 if and only if the statement c holds. To compute  $S^{(1)}$  in isd0, for each  $(v,I) \in \mathcal{S}_p(T^{(0)},\tilde{s}^{(0)})$ , CAT computes  $\mathcal{E}(v=0)$  and conditionally pushes I into a queue of size QU, where QU is an attack parameter. Every time PE elements in  $\mathcal{S}_p(T^{(0)},\tilde{s}^{(0)})$  are checked, where PE is another attack parameter such that PE  $\geq$  QU, for each I in the queue, CAT computes  $v=\tilde{s}^{(1)}-T^{(1)}[I]$ ,  $\mathcal{E}(\mathrm{wt}(v)=t-p)$  and conditionally stores (I,v) into the solution buffer. After all the elements in the queue are checked, the queue is cleared so that the next PE elements in  $\mathcal{S}_p(T^{(0)},\tilde{s}^{(0)})$  can be processed.

Note that every I such that  $(0,I) \in \mathcal{S}_p(T^{(0)},\tilde{s}^{(0)})$  will be pushed into the queue, but it might be kicked out from the queue, which is why  $S^{(1)}$  might not be equal to the corresponding superset. The attack parameters QU and PE allow these circuits to trade efficiency (in terms of cost) for success probability, and vice versa. See Appendix J.1 for how CAT predicts queue-loss probabilities.

**5.11. Search phase in isd1.** In each search phase of isd1, to find collisions between  $S_L$  and  $S_R$ , CAT first sorts the elements in  $\{(v,I,0) \mid (v,I) \in S_L\}$  and  $\{(v,I,1) \mid (v,I) \in S_R\}$  together, using the following ordering: (v,I,b) > (v',I',b') means that (1) v > v' in lexicographic order or (2) v = v' and b' > b. Let the sorted list be L, and, for an attack parameter WI > 0, define

$$S_{L,R} = \left\{ (L[i], L[i+d]) \mid d \in \{1, \dots, WI\} \right\}.$$

For each element  $((v,I,b),(v',I',b')) \in S_{L,R}$  in a random order, CAT computes  $\mathcal{E}(v=v',b\neq b')$  and conditionally pushes (I,I') into a queue of size QU. Every time PE elements in  $S_{L,R}$  are checked, for each (I,I') in the queue, CAT computes  $w=s^{(1)}-(T_L^{(1)}[I]+T_R^{(1)}],\mathcal{E}(\mathrm{wt}(w)=t-2p)$  and conditionally stores (I,I',w) into the solution buffer. After all the elements in the queue are checked, the queue is cleared so that the next PE elements in  $S_{L,R}$  can be processed.

The use of queues is as in isd0; the WI parameter provides another tradeoff between probability and cost. See Appendix J.2 for how CAT predicts window-loss probabilities.

**5.12. Search phase in isd2.** In each search phase in isd2,  $S_L^{(0)}$ ,  $S_R^{(0)}$ , and  $\hat{S}_R^{(0)}$  are generated for each  $\Delta \in S_\Delta \subseteq \mathbb{F}_2^{\ell_0}$ . As  $S_L^{(0)}$  is independent of  $\Delta$ , it is generated at the beginning of the search phase and simply reused for all  $\Delta$ 's.  $S_R^{(0)}$  and  $\hat{S}_R^{(0)}$ , unlike  $S_L^{(0)}$ , can change for different  $\Delta$  's. To save bit operations for generating  $S_R^{(0)}$ and  $\hat{S}_{R}^{(0)}$ , CAT uses a Gray code to ensure that any two consecutive  $\Delta$ 's differ in only 1 bit. In this way, whenever a new  $\Delta$  is used, it takes only 1 NOT to update each element in  $S_{R}^{(0)}$  and  $\hat{S}_{R}^{(0)}$ .

The computations of  $S^{(2)}$  from  $S^{(1)}$  and  $\hat{S}^{(1)}$ , of  $S^{(1)}$  from  $S_{L}^{(0)}$  and  $\hat{S}_{R}^{(0)}$ , and of  $\hat{S}^{(1)}$  from  $S_{L}^{(0)}$  and  $\hat{S}^{(0)}$  in isd2 work the same way

as the computation of  $S^{(1)}$  from  $S_L$  and  $S_R$  in isd1, using separate WI1, QU1, PE1, WI2, QU2, PE2 parameters for the two levels.

#### **Numerical results** 6

This section presents and compares various numbers produced by this paper's formalization. Section 6.1 compares observed effectiveness of the simulated circuits for various small n to predicted effectiveness, finding a very close match. Section 6.2 quantifies what the predictions say at cryptographic sizes, specifically regarding (1) the security levels of the Classic McEliece parameter lists from [8] and (2) comparisons among ISD algorithms.

Appendix L considers ways that inaccuracies could have appeared in the predictions while avoiding detection by the simulations in Section 6.1.

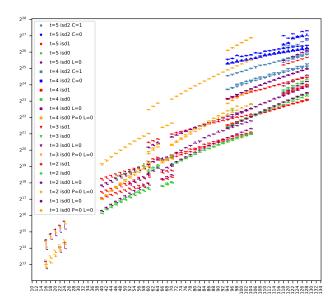

**6.1. Comparing simulations to predictions.** The CAT package includes an isdsims.py script to run the experiments described below, and an isdsims-graph.py script to convert the results of the experiments into the graph shown in Figure 4.

The experiments are as follows:

- For each  $n \in \{16, 18, 20, ..., 128\}$ , and for each integer  $t \ge 1$ such that  $k = n - t \lceil \lg n \rceil$  satisfies  $0.7 \le k/n \le 0.8$ , use searchparams to heuristically search for parameters for isd0 with p = 0 and  $\ell = 0$ , isd0 with  $\ell = 0$ , isd0 without restrictions, isd1, isd2 with C = 0, and isd2 with C = 1, in each case with FW chosen as 1 and with (IT, RE) chosen in three different ways: (1,1) or (2,1) or (4,4). This produces a sequence of attack parameter lists.

- For each attack parameter list, use circuitcost to compare the observed cost of the simulated circuit to the predicted cost. This raises an alert if the costs are not identical. (No cost alerts appeared.)

- Also, for each attack parameter list, use circuitprob with trialfactor = 100000 and probfactor = 100 to run many experiments with the simulated circuit and compare the observed success probability to the predicted success probability. Setting probfactor = 100 skips circuits with success probability below 1%; concretely, this means skipping some of the larger isd0 circuits.

The results of the probability comparison are shown in the graph in Figure 4. Each circuit produces one dot in the graph, where the horizontal position of the dot is *n*, the shape of the dot indicates t, and the vertical position of the dot is the ratio between circuit cost and observed success probability. An arrow coming from the

Figure 4: Accuracy of predictions of success probability for various attack circuits for small n. Horizontal axis: n. Vertical axis: circuit cost divided by success probability. Each dot shows experimentally observed successes from the simulated circuit with trialfactor = 100000. The arrow from the left of the dot shows the probability prediction. The arrow from the right of the dot shows a simplified probability prediction without a collision correction.

left of the dot shows the ratio between circuit cost and predicted success probability. An arrow coming from the right of the dot shows the ratio between circuit cost and a simplified prediction of success probability, where the simplification omits a correction for collisions; see Appendix K. The two predictions differ by at most  $\binom{n-k}{t} - 1/2^{n-k}$ , which converges rapidly to 0 as *n* and *t* increase.

For small n with t = 1, the graph shows the prediction understating circuit effectiveness by about 0.1 bits (while the simplified prediction overstates circuit effectiveness), with a maximum error below 0.2 bits. The prediction generally becomes more accurate as *n* and *t* increase within the range of the graph, although the arrival of isd2 for t = 4 is again accompanied by measurable deviations. Note that if predicted success probabilities are accurate then, with trialfactor = 100000, the ratio between observed success probability and actual success probability will have standard deviation considerably below 1%.

As expected, the graph (of observed values and of predicted values) shows large jumps upwards as t increases from 1 to 2 to 3 to 4 to 5, and gentler increases with n. For each problem parameter with  $t \le 3$ , the smallest cost/probability ratios in the graph are from isd0; isd1 begins to take over at t = 4. There are a few cases where the graph shows searchparams finding slightly better results when *n* is increased; presumably more comprehensive parameter searches would move more dots slightly downwards.

**6.2. Predictions for cryptographic sizes.** The CAT package includes scripts isdpredict1.py and isdpredict2.py to search for attack parameters for cryptographic sizes, along with a script isdpredict-table.py to turn the results into Table 1 below.

The Classic McEliece documentation selects five parameter lists (n, k, t), namely (3488, 2720, 64); (4608, 3360, 96); (6688, 5024, 128); (6960, 5413, 119); (8192, 6528, 128). CAT takes 47 hours on a dual EPYC 7742 (with Core Performance Boost disabled) to collect data for all of these. The results for 6688 and 6960 are almost identical; to save space, the table shows just the smaller size 6688. For comparison, the script also covers (n, k, t) = (1284, 1020, 24), the size of the largest challenge broken in [57] using isd2, and (n, k, t) = (1347, 1047, 25), the size of a larger challenge broken in 2023 using isd1 (see [23]); the table includes 1284.

For each parameter list, the table reports, for various circuits, the predicted ratio between circuit cost and success probability. Table entries in columns isd through *C* indicate attack constraints.

Table 1 is split into several sections. The first section, just one row, is Prange's original ISD algorithm: isd0 with RE = 1,  $\ell$  = 0, and p = 0. The next section is for general isd0, including the Lee–Brickell use of p and Leon's use of  $\ell$ . The next section is isd1, including collision searches from Stern and Dumer. All of this is still from the 1980s, except that random walks at the time were limited to Omura's X = 1 for isd0. Random walks do not matter for large p, p', p'' but provide an interesting speedup for small p, p', p''; see the table rows with and without the RE = 1 restriction.

There are, finally, three sections for i sd2. The first is for p' = 2p'' with C = 0, as in the MMT paper, although this paper does better using random walks and many speedups in subroutines. The second is for p' = 2p'' - 2 with C = 0, an example of the BJMM paper with two levels, although again this paper includes more improvements. The third is for C = 1, where the CAT analysis appears to be the first analysis in the literature; note that the C = 1 attack ignores p', so taking p' < 2p'' would make no difference here.

Each section beyond the first is split into lines with different values of p or p' or p'', the parameter controlling the starting list sizes, so that the reader can see the drop in circuit costs as this parameter increases to an optimal value. The minimal cost in each section is highlighted in blue.

The asymptotics in the literature already indicate that the optimum for this parameter gradually increases with n in the McEliece context (see, e.g., [31, Sections 4–5]). CAT provides precise, fully defined data on this point for concrete sizes.

The full attack parameters for each table row are defined as follows. Starting from the parameter restrictions shown in the table plus FW = 1, the isdpredict1.py script runs searchparams for IT = 1 to find an initial list of parameters. For each  $r \in \{0,1,\ldots,24\}$ , the isdpredict2.py script then runs searchparams again to search for (X,Y) subject to RE =  $2^r$ , IT =  $2^{r+16}$  (this ensures that the reset costs will be counted within a  $2^{-16}$  error), and all other parameters matching the output from isdpredict1.py. The lowest cost/probability ratio across r is used for the table, except for the RE = 1 rows, which use r = 0.

Compared to the original Prange algorithm (first row), the smallest exponent shown in the table is 15% lower for n=3488, reflecting the overall impact of many years of algorithmic improvements. It is remarkable that most of this change was already achieved in

Table 1: Logarithm base 2, rounded to 2 digits, of the ratio between predicted cost and predicted success probability for various attack circuits. See text for details.

| isd    | RE | $\ell$ | р      | p'       | $p^{\prime\prime}$ | C      | 1284           | 3488             | 4608             | 6688             | 8192             |

|--------|----|--------|--------|----------|--------------------|--------|----------------|------------------|------------------|------------------|------------------|

| 0      | 1  | 0      | 0      |          |                    |        | 85.99          | 177.26           | 221.14           | 299.99           | 338.10           |

| 0      |    | 0      | 0      |          |                    |        | 78.62          | 168.34           | 211.56           | 290.00           | 328.15           |

| 0      | 1  | 0      | 1      |          |                    |        | 79.39          | 169.34<br>163.70 | 213.02           | 291.29           | 329.02           |

| 0      | 1  | 0      | 1<br>2 |          |                    |        | 75.24<br>78.13 | 165.70           | 206.54<br>209.62 | 284.50<br>287.59 | 322.49<br>325.62 |

| 0      | 1  | 0      | 2      |          |                    |        | 78.13          | 166.63           | 209.52           | 287.50           | 325.56           |

| 0      |    | 0      | 3      |          |                    |        | 81.53          | 170.14           | 213.13           | 291.11           | 329.17           |

| 0      | 1  | Ŭ      | 1      |          |                    |        | 80.47          | 170.53           | 214.24           | 292.50           | 330.21           |

| 0      |    |        | 1      |          |                    |        | 74.46          | 163.06           | 205.87           | 283.94           | 321.87           |

| 0      | 1  |        | 2      |          |                    |        | 76.27          | 165.12           | 208.51           | 286.32           | 323.72           |

| 0      |    |        | 2      |          |                    |        | 72.54          | 159.93           | 202.30           | 279.88           | 317.66           |

| 0      |    |        | 3      |          |                    |        | 75.89          | 163.31           | 205.68           | 283.34           | 321.17           |

| 1      | 1  |        |        | 1        |                    |        | 76.83          | 165.65           | 209.02           | 286.83           | 324.27           |

| 1      | 1  |        |        | 1        |                    |        | 71.11          | 158.39           | 201.17           | 278.63           | 316.07           |

| 1<br>1 | 1  |        |        | 2 2      |                    |        | 71.66<br>71.48 | 157.33<br>156.96 | 199.60<br>198.93 | 276.39<br>275.71 | 313.45<br>312.97 |

| 1      |    |        |        | 3        |                    |        | 73.16          | 157.43           | 199.27           | 275.53           | 312.47           |

| 1      |    |        |        | 4        |                    |        | 75.00          | 157.15           | 199.69           | 275.41           | 312.03           |

| 1      |    |        |        | 5        |                    |        | 77.19          | 158.64           | 200.24           | 275.41           | 311.69           |

| 1      |    |        |        | 6        |                    |        | 80.73          | 159.48           | 200.91           | 275.55           | 311.52           |

| 1      |    |        |        | 7        |                    |        | 87.30          | 160.50           | 201.74           | 275.82           | 311.44           |

| 1      |    |        |        | 8        |                    |        | 93.88          | 161.68           | 202.71           | 276.23           | 311.50           |

| 1      |    |        |        | 9        |                    |        | 100.26         | 163.03           | 203.83           | 276.74           | 311.69           |

| 2      | 1  |        |        | 2        | 1                  | 0      | 72.37          | 158.93           | 201.45           | 278.24           | 315.21           |

| 2      |    |        |        | 2        | 1                  | 0      | 70.95          | 156.26           | 198.61           | 275.13           | 312.22           |